Nonetheless, though personal computer chips will never melt away a literal gap in your pocket (although they do get sizzling more than enough to

fry an egg), they nonetheless have to have a great deal of present to run the purposes we use each day. Consider the info-middle SoC: On normal, it really is consuming two hundred W to deliver its transistors with about one to two volts, which implies the chip is drawing one hundred to two hundred amperes of present from the voltage regulators that source it. Your usual fridge draws only six A. Substantial-end cell phones can draw a tenth as a lot electrical power as info-middle SoCs, but even so that’s nonetheless about 10–20 A of present. That is up to three refrigerators, in your pocket!

Offering that present to billions of transistors is rapidly getting to be a person of the major bottlenecks in large-overall performance SoC style. As transistors carry on to be manufactured tinier, the interconnects that source them with present need to be packed at any time closer and be manufactured at any time finer, which raises resistance and saps electrical power. This won’t be able to go on: Without a major change in the way electrons get to and from devices on a chip, it will never make a difference how a lot scaled-down we can make transistors.

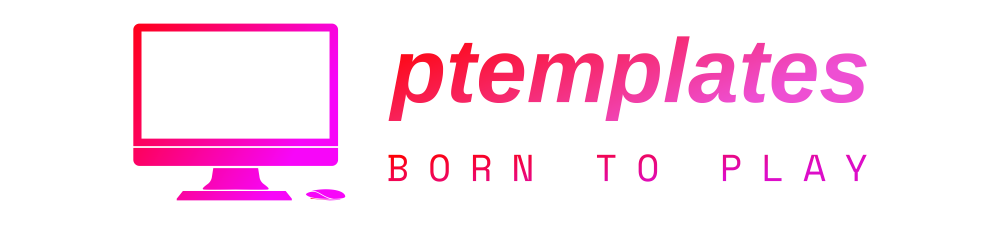

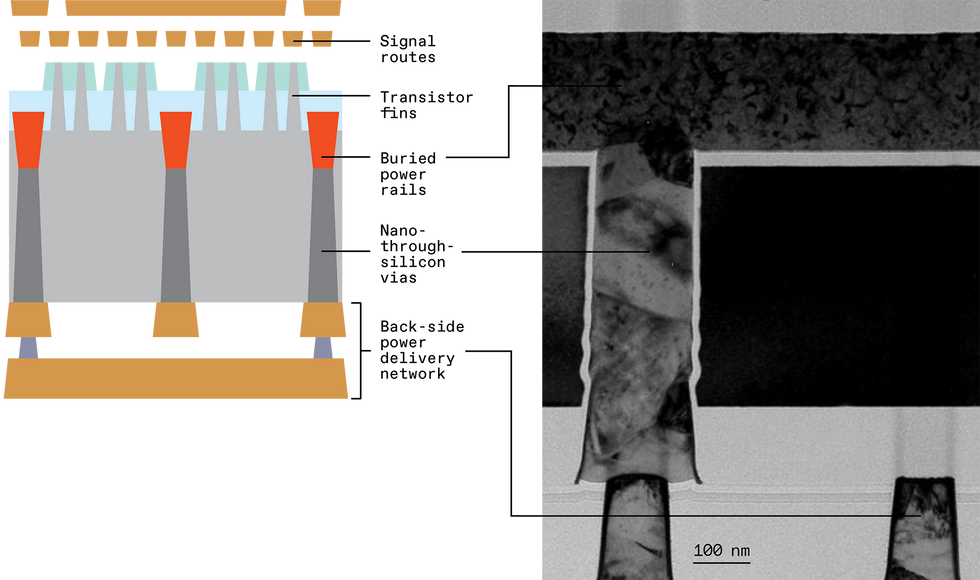

In present day processors the two alerts and electrical power arrive at the silicon [mild grey] from previously mentioned. New technological know-how would separate those capabilities, saving electrical power and making much more place for sign routes [ideal].Chris Philpot

The good thing is, we have a promising resolution: We can use a facet of the silicon that’s prolonged been overlooked.

Electrons have to vacation a prolonged way to get from the source that is producing them to the transistors that compute with them. In most electronics they vacation together the copper traces of a printed circuit board into a package deal that holds the SoC, by way of the solder balls that link the chip to the

package deal, and then by way of on-chip interconnects to the transistors by themselves. It is really this very last stage that definitely matters.

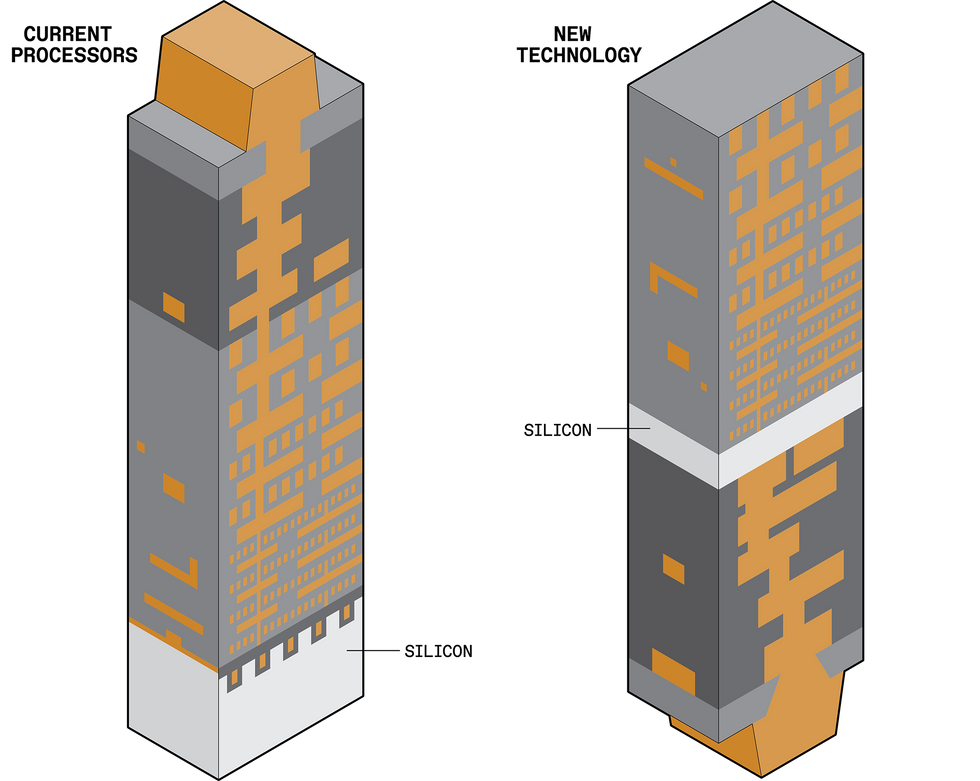

To see why, it allows to understand how chips are manufactured. An SoC starts off as a bare piece of large-top quality, crystalline silicon. We first make a layer of transistors at the really top rated of that silicon. Following we backlink them with each other with steel interconnects to type circuits with practical computing capabilities. These interconnects are formed in levels termed a stack, and it can get a 10-to-20-layer stack to provide electrical power and info to the billions of transistors on present day chips.

Those levels closest to the silicon transistors are skinny and small in purchase to link to the very small transistors, but they increase in dimensions as you go up in the stack to bigger amounts. It is really these amounts with broader interconnects that are greater at delivering electrical power mainly because they have fewer resistance.

Currently, the two electrical power and alerts arrive at transistors from a network of interconnects previously mentioned the silicon (the “front facet”). But increasing resistance as these interconnects are scaled down to at any time-finer dimensions is making that plan untenable.Chris Philpot

You can see, then, that the steel that powers circuits—the electrical power shipping and delivery network (PDN)—is on top rated of the transistors. We refer to this as front-facet electrical power shipping and delivery. You can also see that the electrical power network unavoidably competes for house with the network of wires that provides alerts, mainly because they share the exact set of copper assets.

In purchase to get electrical power and alerts off of the SoC, we commonly link the uppermost layer of metal—farthest absent from the transistors—to solder balls (also termed bumps) in the chip package deal. So for electrons to arrive at any transistor to do practical operate, they have to traverse 10 to 20 levels of progressively slender and tortuous steel until eventually they can ultimately squeeze by way of to the really very last layer of area wires.

This way of distributing electrical power is basically lossy. At each stage together the path, some electrical power is dropped, and some need to be made use of to control the shipping and delivery alone. In present day SoCs, designers commonly have a funds that lets reduction that potential customers to a 10 p.c reduction in voltage in between the package deal and the transistors. Hence, if we strike a full performance of ninety p.c or bigger in a electrical power-shipping and delivery network, our types are on the ideal keep track of.

Traditionally, these types of efficiencies have been achievable with fantastic engineering—some might even say it was simple in contrast to the challenges we facial area nowadays. In present day electronics, SoC designers not only have to handle increasing electrical power densities but to do so with interconnects that are losing electrical power at a sharply accelerating charge with each individual new generation.

You can style a back-facet electrical power shipping and delivery network that’s up to seven moments as effective as the regular front-facet network.

The increasing lossiness has to do with how we make nanoscale wires. That approach and its accompanying supplies trace back to about 1997, when IBM commenced to make interconnects out of copper as a substitute of aluminum, and the business shifted together with it. Up until eventually then aluminum wires had been good conductors, but in a handful of much more steps together the

Moore’s Regulation curve their resistance would before long be much too large and turn into unreliable. Copper is much more conductive at modern-day IC scales. But even copper’s resistance commenced to be problematic as soon as interconnect widths shrank below one hundred nanometers. Currently, the smallest created interconnects are about 20 nm, so resistance is now an urgent difficulty.

It allows to image the electrons in an interconnect as a comprehensive set of balls on a billiards table. Now consider shoving them all from a person end of the table toward one more. A handful of would collide and bounce against each individual other on the way, but most would make the journey in a straight-ish line. Now consider shrinking the table by half—you’d get a great deal much more collisions and the balls would go much more slowly. Following, shrink it all over again and increase the range of billiard balls tenfold, and you happen to be in something like the scenario chipmakers facial area now. True electrons do not collide, automatically, but they get close more than enough to a person one more to impose a scattering drive that disrupts the move by way of the wire. At nanoscale dimensions, this potential customers to vastly bigger resistance in the wires, which induces important electrical power-shipping and delivery reduction.

Raising electrical resistance is not a new challenge, but the magnitude of increase that we are looking at now with each individual subsequent approach node is unparalleled. Additionally, regular techniques of taking care of this increase are no for a longer period an option, mainly because the producing regulations at the nanoscale impose so a lot of constraints. Long gone are the days when we could arbitrarily increase the widths of certain wires in purchase to fight increasing resistance. Now designers have to adhere to certain specified wire widths or else the chip might not be manufacturable. So, the business is faced with the twin problems of bigger resistance in interconnects and fewer place for them on the chip.

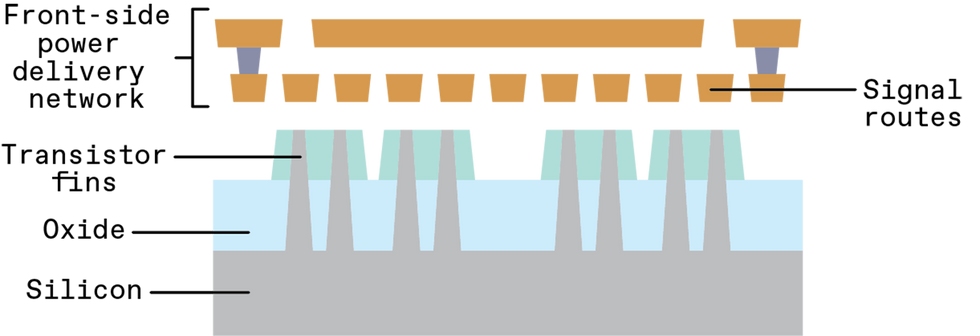

There is one more way: We can exploit the “empty” silicon that lies below the transistors. At Imec, exactly where authors Beyne and Zografos operate, we have pioneered a producing notion termed “buried electrical power rails,” or BPR. The procedure builds electrical power connections below the transistors as a substitute of previously mentioned them, with the aim of producing fatter, fewer resistant rails and freeing house for sign-carrying interconnects previously mentioned the transistor layer.

To lessen the resistance in electrical power shipping and delivery, transistors will tap electrical power rails buried within just the silicon. These are somewhat big, reduced-resistance conductors that numerous logic cells could link with.Chris Philpot

To build BPRs, you first have to dig out deep trenches below the transistors and then fill them with steel. You have to do this ahead of you make the transistors by themselves. So the steel alternative is critical. That steel will need to endure the processing steps made use of to make large-top quality transistors, which can arrive at about one,000 °C. At that temperature, copper is molten, and melted copper could contaminate the total chip. We’ve for that reason experimented with ruthenium and tungsten, which have bigger melting details.

Due to the fact there is so a lot unused house below the transistors, you can make the BPR trenches huge and deep, which is best for delivering electrical power. In comparison to the skinny steel levels instantly on top rated of the transistors,

BPRs can have one/20 to one/thirty the resistance. That implies that BPRs will successfully allow you to provide much more electrical power to the transistors.

Additionally, by relocating the electrical power rails off the top rated facet of the transistors you totally free up place for the sign-carrying interconnects. These interconnects type basic circuit “cells”—the smallest circuit units, these types of as SRAM memory bit cells or uncomplicated logic that we use to compose much more advanced circuits. By working with the house we have freed up, we could shrink those cells by

sixteen p.c or much more, and that could eventually translate to much more transistors per chip. Even if characteristic dimensions stayed the exact, we might nonetheless thrust Moore’s Regulation a person phase further more.

Regretably, it appears like burying area electrical power rails on your own will never be more than enough. You nonetheless have to convey electrical power to those rails down from the top rated facet of the chip, and that will value performance and some reduction of voltage.

Long gone are the days when we could arbitrarily increase the widths of certain wires in purchase to fight increasing resistance.

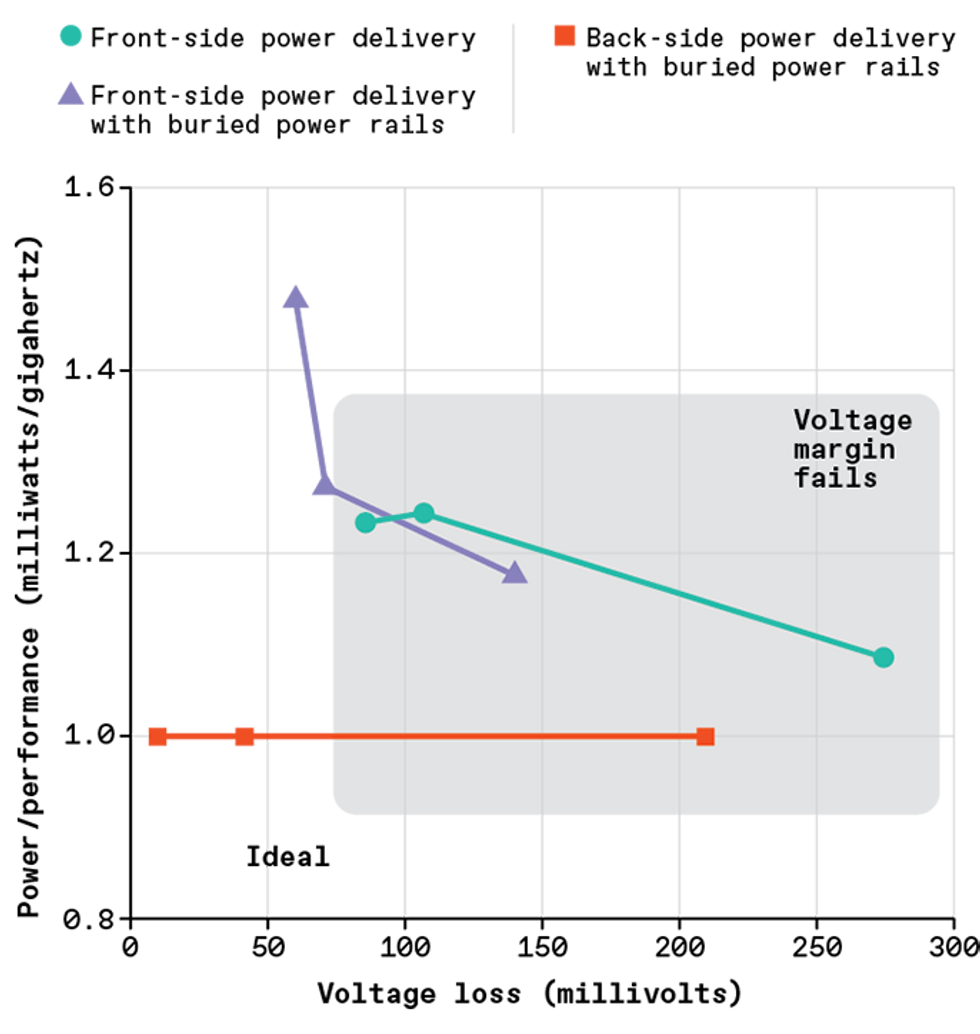

Scientists at Arm, which include authors Cline and Prasad, ran a simulation on a person of their CPUs and located that, by by themselves, BPRs could allow you to build a forty p.c much more effective electrical power network than an common front-facet electrical power shipping and delivery network. But they also located that even if you made use of BPRs with front-facet electrical power shipping and delivery, the all round voltage delivered to the transistors was not large more than enough to sustain large-overall performance operation of a CPU.

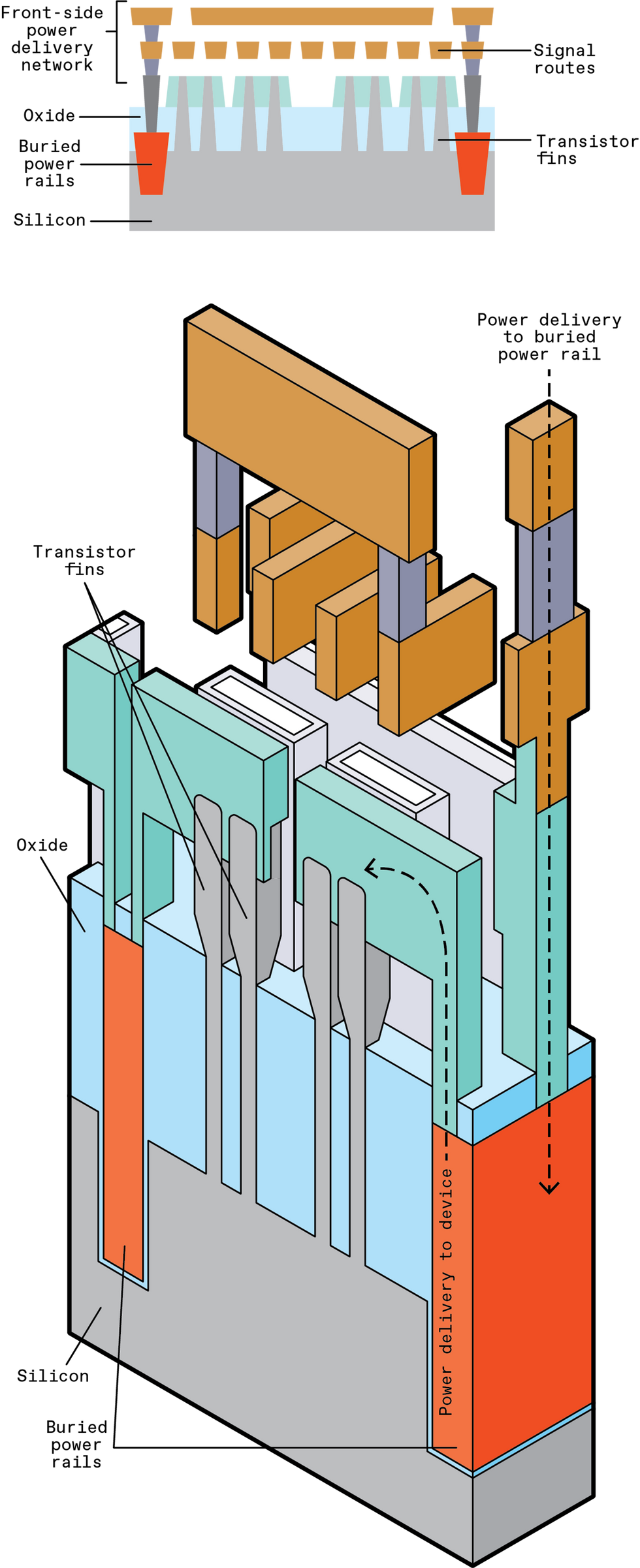

The good news is, Imec was simultaneously acquiring a complementary resolution to further more make improvements to electrical power shipping and delivery: Shift the total electrical power-shipping and delivery network from the front facet of the chip to the back facet. This resolution is termed “back-facet electrical power shipping and delivery,” or much more usually “back-facet metallization.” It will involve thinning down the silicon that is underneath the transistors to five hundred nm or fewer, at which issue you can generate nanometer-dimensions “by way of-silicon vias,” or

nano-TSVs. These are vertical interconnects that can link up by way of the back facet of the silicon to the base of the buried rails, like hundreds of very small mineshafts. The moment the nano-TSVs have been made below the transistors and BPRs, you can then deposit supplemental levels of steel on the back facet of the chip to type a finish electrical power-shipping and delivery network.

Expanding on our earlier simulations, we at Arm located that just two levels of thick back-facet steel was more than enough to do the occupation. As prolonged as you could house the nano-TSVs closer than two micrometers from each individual other, you could style a back-facet PDN that was 4 moments as effective as the front-facet PDN with buried electrical power rails and seven moments as effective as the regular front-facet PDN.

The back-facet PDN has the supplemental advantage of getting bodily separated from the sign network, so the two networks no for a longer period compete for the exact steel-layer assets. There’s much more place for each individual. It also implies that the steel layer characteristics no for a longer period need to be a compromise in between what electrical power routes choose (thick and huge for reduced resistance) and what sign routes choose (skinny and slender so they can make circuits from densely packed transistors). You can simultaneously tune the back-facet steel levels for electrical power routing and the front-facet steel levels for sign routing and get the finest of the two worlds.

Transferring the electrical power shipping and delivery network to the other facet of the silicon—the “back facet”—reduces voltage reduction even much more, mainly because all the interconnects in the network can be manufactured thicker to reduce resistance. What is much more, eliminating the electrical power-shipping and delivery network from previously mentioned the silicon leaves much more place for sign routes, main to even scaled-down logic circuits and allowing chipmakers squeeze much more transistors into the exact region of silicon.

Chris Philpot/IMEC

In our types at Arm, we located that for the two the regular front-facet PDN and front-facet PDN with buried electrical power rails, we had to sacrifice style overall performance. But with back-facet PDN the CPU was in a position to reach large frequencies

and have electrically effective electrical power shipping and delivery.

You might, of study course, be wondering how you get alerts and electrical power from the package deal to the chip in these types of a plan. The nano-TSVs are the essential right here, much too. They can be made use of to transfer all input and output alerts from the front facet to the back facet of the chip. That way, the two the electrical power and the I/O alerts can be hooked up to solder balls that are positioned on the back facet.

Simulation experiments are a terrific commence, and they present the CPU-style-degree opportunity of back-facet PDNs with BPR. But there is a prolonged road forward to carry these systems to large-volume producing. There are nonetheless important supplies and producing challenges that need to be solved. The finest alternative of steel supplies for the BPRs and nano-TSVs is critical to manufacturability and electrical performance. Also, the large-part-ratio (deep but skinny) trenches wanted for the two BPRs and nano-TSVs are really hard to make. Reliably etching tightly spaced, deep-but-slender options in the silicon substrate and filling them with steel is somewhat new to chip manufacture and is nonetheless something the business is receiving to grips with. Building producing tools and methods that are responsible and repeatable will be essential to unlocking prevalent adoption of nano-TSVs.

Additionally, battery-powered SoCs, like those in your cellphone and in other electrical power-constrained types, by now have a lot much more advanced electrical power-shipping and delivery networks than those we have talked about so significantly. Modern day-day electrical power shipping and delivery separates chips into numerous electrical power domains that can run at diverse voltages or even be turned off completely to conserve electrical power. (See ”

A Circuit to Strengthen Battery Lifestyle,” IEEE Spectrum, August 2021.)

In assessments of numerous types working with three versions of electrical power shipping and delivery, only back-facet electrical power with buried electrical power rails [crimson] gives more than enough voltage without compromising overall performance.Chris Philpot

Hence, back-facet PDNs and BPRs are eventually heading to have to do a lot much more than just proficiently provide electrons. They’re heading to have to specifically control exactly where electrons go and how a lot of of them get there. Chip designers will not want to get numerous steps backward when it arrives to chip-degree electrical power style. So we will have to simultaneously enhance style and producing to make confident that BPRs and back-facet PDNs are greater than—or at minimum appropriate with—the electrical power-saving IC tactics we use nowadays.

The potential of computing relies upon upon these new producing tactics. Energy usage is critical irrespective of whether you happen to be stressing about the cooling monthly bill for a info middle or the range of moments you have to cost your smartphone each individual day. And as we carry on to shrink transistors and ICs, delivering electrical power will become a important on-chip challenge. BPR and back-facet PDNs might nicely respond to that challenge if engineers can conquer the complexities that appear with them.

This post appears in the September 2021 print difficulty as “Energy From Below.”